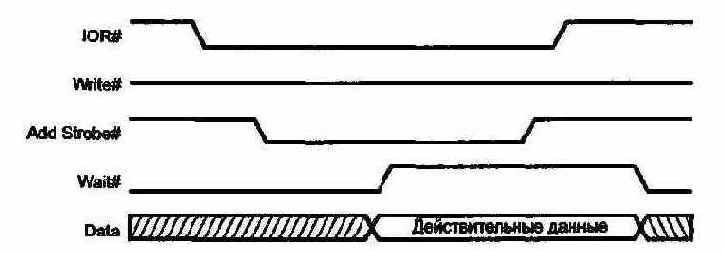

Адресный цикл чтения ЕРР

Рисунок 1.6. Адресный цикл чтения ЕРР

Главной отличительной чертой ЕРР является выполнение внешней передачи во время одного процессорного цикла вво-

да/вывода. Это позволяет достигать высоких скоростей об- мена (0,5...2 Мбайт/с). ПУ, подключенное к параллельному порту ЕРР, может работать со скоростью устройства, под- ключаемого через слот ISA. Протокол блокированного кви- тирования (interlocked handshakes) позволяет автоматичес- ки настраиваться на скорость обмена, доступную и хосту, и ПУ. ПУ может регулировать длительность всех фаз обмена с помощью всего лишь одного сигнала Wait#. Протокол ав- томатически подстраивается под длину кабеля - вносимые задержки приведут только к удлинению цикла. Поскольку кабели, соответствующие IEEE 1284 (см. выше), имеют оди- наковые волновые свойства для разных линий, нарушения передачи, связанного с "состязаниями" сигналов, происхо- дить не должно. При подключении сетевых адаптеров или внешних дисков к ЈPP-nopTy можно наблюдать непривыч- ное явление: снижение производительности по мере удли- нения интерфейсного кабеля.

Естественно, ПУ не должно "подвешивать" процессор на шинном цикле обмена. Это гарантирует механизм тайм-аутов PC, который принудительно завершает любой цикл обмена, длящийся более 15 мкс. В ряде реализации ЕРР за тайм-аутом интерфейса следит сам адаптер - если ПУ не отвечает в те- чение определенного времени (5 мкс), цикл прекращается и в дополнительном (не стандартизованном) регистре состоя- ния адаптера фиксируется ошибка.

Устройства с интерфейсом ЕРР, разработанные до принятия IEEE 1284, отличаются началом цикла: строб DataStb# или AddrStb# устанавливается независимо от состояния WAIT#. Это означает, что ПУ не может задержать начало следующе- го цикла (хотя может растянуть его на требуемое время). Такая спецификация называется ЕРР 1.7 (предложена Xircom). Именно она применялась в контроллере 82360. Периферия, совместимая с ЕРР 17, будет нормально рабо- тать и с контроллером ЕРР 1284, но периферия в стандарте ЕРР 1284 может отказаться работать с контроллером ЕРР 1.7.

С программной точки зрения контроллер ЯРР-порта выгля- дит просто (см. табл. 1.7). К трем регистрам стандартного порта, имеющим смещение 0, 1 и 2 относительно базового

адреса порта, добавлены два регистра (ЕРР Address Port и ЕРР Data Port), чтение и запись в которые вызывает генера- цию связанных внешних циклов.

Назначение регистров стандартного порта сохранено для со- вместимости fPP-порта с ПУ и ПО, рассчитанными на при- менение программно-управляемого обмена. Поскольку сиг- налы квитирования адаптером вырабатываются аппаратно, при записи в регистр управления СП биты 0, 1 и 3, соответ- ствующие сигналам Strobeft, AutoFeed# и Selecting должны иметь нулевые значения. Программное вмешательство мог- ло бы нарушить последовательность квитирования. Некото- рые адаптеры имеют специальные средства защиты (ЕРР Protect), при включении которых программная модифика- ция этих бит блокируется.

Использование регистра данных ЕРР позволяет осуществлять передачу блока данных с помощью одной инструкции REP INSB или REP OUTSB. Некоторые адаптеры допускают 16-/ 32-битное обращение к регистру данных ЕРР. При этом адап- тер просто дешифрует адрес со смещением в диапазоне 4-7 как адрес регистра данных ЕРР, но процессору сообщает о раз- рядности 8 бит. Тогда 16- или 32-битное обращение по ад- ресу регистра данных ЕРР приведет к автоматической гене- рации двух или четырех шинных циклов по нарастающим адресам, начиная со смещения 4. Эти циклы будут выпол- няться быстрее, чем то же количество одиночных циклов. Таким образом обеспечивается производительность до 2 Мбайт/с, достаточная для адаптеров локальных сетей, вне- шних дисков, стриммеров и CD-ROM. Адресные циклы ЕРР всегда выполняются только в однобайтном режиме.

Важной чертой ЕРР является то, что обращение процессора к ПУ осуществляется в реальном времени - нет буфериза- ции. Драйвер способен отслеживать состояние и подавать команды в точно известные моменты времени. Циклы чте- ния и записи могут чередоваться в произвольном порядке или идти блоками.

Такой тип обмена удобен для регистро- ориентированных ПУ или ПУ, работающих в реальном вре- мени, - сетевых адаптеров, устройств сбора информации и управления и т. п.

Режим ЕСР

Протокол ЕСР (Extended Capability Port - порт с расши- ренными возможностями) был предложен Hewlett Packard и Microsoft для связи с ПУ типа принтеров или сканеров. Как и ЕРР, данный протокол обеспечивает высокопроизво- дительный двунаправленный обмен данными хоста с ПУ.

Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

циклы записи и чтения данных;

командные циклы записи и чтения.

Командные циклы подразделяются на два типа: передачу канальных адресов и передачу счетчика RLC (Run-Length Count).

В отличие от ЕРР, вместе с протоколом ЕСР сразу появился стандарт на программную (регистровую) модель его адапте- ра, изложенный в документе "The IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard" ком- пании Microsoft. Этот документ определяет свойства прото- кола, не заданные стандартом IEEE 1284:

компрессию данных хост-адаптером по методу RLE;

буферизацию FIFO для прямого и обратного каналов;

применение DMA и программного ввода/вывода.

Компрессия в реальном времени по методу RLE (Run-Length Encoding) позволяет достичь коэффициента сжатия 64:1 при передаче растровых изображений, которые имеют длинные строки повторяющихся байт. Компрессию можно использо- вать, только если ее поддерживает и хост, и ПУ.

Канальная адресация ЕСР применяется для адресации мно- жества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/ модем, подключаемом только к одному параллельному пор- ту, возможен одновременный прием факса и печать на прин- тере. В режиме SPP, если принтер установит сигнал занятос- ти, канал будет занят данными, пока принтер их не примет. В режиме ЕСР программный драйвер просто адресуется к другому логическому каналу того же порта.

Протокол ЕСР переопределяет сигналы SPP (табл. 1.8).

|

Контакт |

Сигнал SPP |

Имя в ЕСР |

I/O |

Описание |

|

1 |

Strobe" |

HostClk |

0 |

Используется в паре с PeriphAck для передачи в прямом направлении (вывод) |

|

14 |

AutoLF# |

HostAck |

о |

Указывает тип цикла (команда/данные) при передаче в прямом на- правлении. Использует- ся в паре с PeriphClk для передачи в обратном на- правлении |

|

17 |

Selecting |

1284Active |

о |

Высокий уровень указы- вает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

|

16 |

lnit# |

о |

Низкий уровень пере- ключает канал на пере- дачу в обратном направ- лении |

|

|

ReverseRequest* |

||||

|

10 |

Ack# |

PeriphQk |

1 |

Используется в паре с HostAck для передачи в обратном направлении |

|

11 |

Busy |

PeriphAck |

I |

Используется в паре с HostClk для передачи в обратном направлении. Индицирует тип коман- да/данные при передаче в обратном направлении |

|

12 |

PaperEnd |

AckReverse# |

I |

Переводится в низкий уровень как подтверж- дение сигналу ReverseRequest# |

|

13 |

Select |

Xflag* |

I |

Флаг расширяемости |

|

15 |

Error# |

PeriphRequest#* |

I |

Устанавливается ПУ для указания на доступность (наличие) обратного ка- нала передачи* |

|

2-9 |

Data [0:7] |

Data [0:7] |

I/O |

Двунаправленный канал данных |

Адаптер ЕСР тоже генерирует внешние протокольные сиг- налы квитирования аппаратно, но его работа существенно отличается от режима ЕРР.

На Рисунок 1.7а приведена диаграмма двух циклов прямой пе- редачи: за циклом данных следует командный цикл. Тип цлкла задается уровнем на линии HostAck: в цикле данных - вы- сокий, в командном цикле - низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отли- чительным признаком является бит 7 (старший): если он нулевой, то биты 0-6 содержат счетчик RLE (0-127), если единичный - то канальный адрес. На Рисунок 1.76 показана пара циклов обратной передачи.