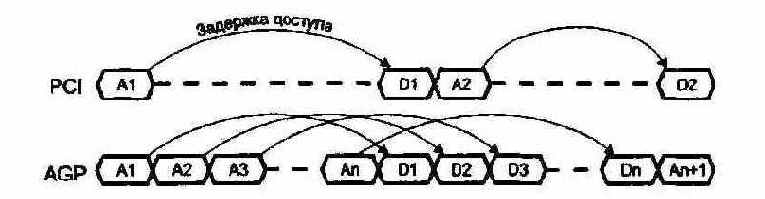

Циклы обращения к памяти РС1 и AGP

Рисунок 4.11. Циклы обращения к памяти РС1 и AGP

Сдвоенная передача данных обеспечивает при частоте 66 МГц пропускную способность до 532 Мбайт/с, что для 32-битной шины неожиданно. В AGP кроме "классического" режима, называемого теперь "х1", в котором за один такт синхрони- зации передается один 4-байтный блок данных, есть режим ".г2", когда блоки данных передаются как по фронту, так и по спаду сигнала синхронизации (как в АТА Ultra DMA). Управление передачей в таком режиме названо Sideband Control (приставка SB к имени сигнала). Заказать режим х2 может только графическая карта, если она его поддержива- ет. При переходе на тактовую частоту 100 МГц пропускная способность повышается до 800 Мбайт/с.

Демультиплексирование (разделение) шины адреса и данных сделано несколько необычным образом. Демультиплексиро- вание подразумевает наличие двух полноразрядных шин - адреса и данных. Однако такой вариант дорог. Поэтому шину адреса в демультиплексированием режиме AGP представля- ют 8 линий SBA (Sideband Address), по которым за три так- та синхронизации передаются четыре байта адреса, длина за- проса (1 байт) и команда (1 байт). За каждый такт передаются по два байта - один по фронту, другой по спаду тактового сигнала. Поддержка демультиплексированной адресации не является обязательной для карты AGP. Требу- ется также поддержка хост-контроллера. Альтернативным способом подачи адреса является обычный - по мультиплек- сированной шине AD.

AGP может реализовать всю пропускную способность 64-бит- ной системы памяти компьютера на процессорах Pentium и выше. При этом возможны конкурирующие обращения к

памяти как со стороны процессора, так и со стороны мостов шин PCI.

Порт AGP может работать как в своем "естественном" ре- жиме с конвейеризацией и сдвоенными передачами, так и в режиме шины PCI. В конвейеризированном режиме, в кото- ром начало цикла отмечается сигналом Р1РЕ#, возможны только обращения к памяти. В режиме PCI циклы начина- ются с сигнала FRAME#, и обращения возможны как к про- странству памяти, так и к пространству ввода/вывода и кон- фигурационному пространству.

Кроме собственно AGP, в порте AGP заложены сигналы шины USB, которую предпо- лагается заводить в монитор. Внешне карты с портом AGP похожи на PCI, но у них используется разъем повышенной плотности с "двухэтажным" (как у EISA) расположением ламелей. Сам разъем располагается дальше от задней кром- ки платы, чем разъем PCI.

Фирма Intel ввела поддержку AGP в чипсеты для процессо- ров Pentium Pro и Pentium II. Однако нет "противопоказа- ний" для применения AGP с Pentium.

AGP строился исключительно для графического акселера- тора. Порт позволяет работать в двух режимах - DMA и исполнения (Executive Mode). В режиме DMA акселератор при вычислениях рассматривает видеопамять как первичную, а когда ее недостаточно, подкачивает данные из основной памяти. При этом для трафика порта характерны длитель- ные блочные передачи. В режиме DIME (Direct Memory Execute) видеопамять и основная память для акселератора равнозначны и располагаются в едином адресном простран- стве. Трафик порта при этом будет насыщен короткими про- извольными запросами.

Отметим, что многие преимущества AGP носят потенциаль- ный характер и могут быть реализованы лишь при поддержке аппаратных средств графического адаптера и ПО. Что каса- ется большой пропускной способности AGP, то следует на- помнить, что в графических адаптерах с памятью WRAM или RDRAM внутренняя скорость обмена данными акселе- ратора с видеопамятью достигает 1,6 Гбайт/с, так что DIME выигрывает только за счет объема доступной памяти.