Обмен с памятью по интерфейсу

Рисунок 7.13. Обмен с памятью по интерфейсу PC: a - запись, б - чтение с текущего адреса, в - чтение с произвольного адреса

Выполнив условие Start,

контроллер передает байт, содер- жащий адрес устройства и признак операции RW,

и ожидает подтверждения. При операции записи следующей посылкой от контроллера будет 8-битный адрес записываемой ячейки, а за ней - байт данных (для микросхем объемом памяти бо- лее 256 байт адрес ячейки посылается двумя байтами). По- лучив подтверждения, контроллер завершает цикл услови- ем Stop, а адресованное устройство может начать свой внутренний цикл записи, во время которого не реагирует на сигналы интерфейса. Контроллер проверяет готовность уст- ройства посылкой команды записи (байт адреса устройства)

и анализом бита подтверждения, формируя затем условие Stop. Если устройство откликнулось битом подтверждения, значит, оно завершило внутренний цикл и готово к следую- щей операции.

Операция считывания

инициируется так же, как и запись, но с признаком RW=\. Возможно чтение по заданному адре- су, по текущему адресу или последовательное. Текущий ад- рес хранится во внутреннем счетчике ведомого устройства, он содержит увеличенный на единицу адрес ячейки, участво- вавшей в последней операции.

Получив команду чтения, устройство дает бит подтвержде- ния и посылает байт данных, соответствующий текущему адресу. Контроллер может ответить подтверждением, тогда устройство пошлет следующий байт (последовательное чте- ние). Если на принятый байт данных контроллер ответит условием Stop, операция чтения завершается (случай чтения по текущему адресу). Начальный адрес для считывания кон- троллер задает фиктивной операцией записи, в которой пе- редается байт адреса устройства и байт адреса ячейки, а после подтверждения приема байта адреса снова формируется ус- ловие Start и передается адрес устройства, но уже с указа- нием на операцию чтения. Так реализуется считывание про- извольной ячейки (или последовательности ячеек).

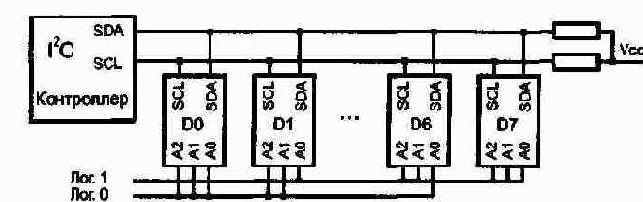

Интерфейс позволяет контроллеру с помощью пары сигна- лов обращаться к любому из 8 однотипных устройств, под- ключенных к данной шине и имеющих уникальный адрес (Рисунок 7.14).

При необходимости увеличения количества уст- ройств возможно подключение групп. При этом допустимо как использование общего сигнала SCL и раздельных сигна- лов SDA (двунаправленных), так и общего сигнала SDA и раздельных однонаправленных сигналов SCL. Для обраще- ния к одной из нескольких микросхем (или устройств), не имеющих выводов для задания собственного адреса, также применяют разделение линий SCL (или SDA).

Протокол PC позволяет нескольким контроллерам исполь- зовать одну шину, определяя коллизии и выполняя арбит- раж. Эти функции реализуются достаточно просто: если два передатчика пытаются установить на линии SDA различные

логические уровни сигналов, то "победит" тот, который ус- тановит низкий уровень. Передатчик следит за уровнями управляемых им сигналов и при обнаружении несоответствия (передает высокий уровень, а "видит" низкий) отказывает- ся от дальнейшей передачи. Устройство может иницииро- вать обмен только при пассивном состоянии сигналов. Кол- лизия может возникнуть лишь при одновременной попытке начала обмена - как только конфликт обнаружен, "проиг- равший" передатчик отключится, а "победивший" продол- жит работу.