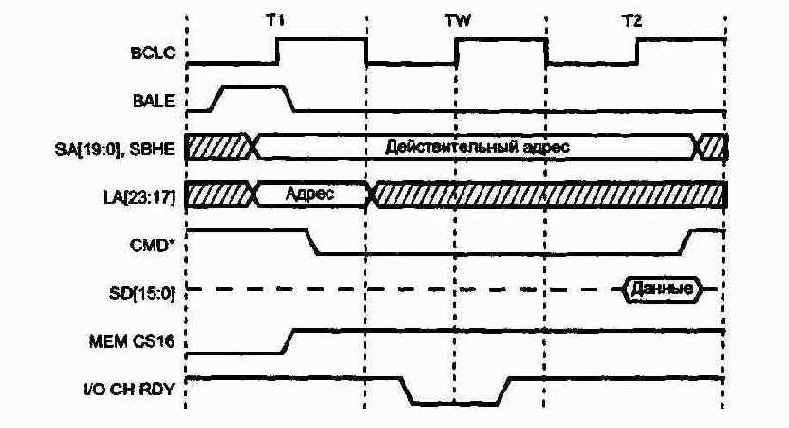

Временные диаграммы циклов чтения или записи на шине ISA

Рисунок 4.5. Временные диаграммы циклов чтения или записи на шине ISA

В каждом из рассматриваемых циклов активными (с низ- ким уровнем) могут быть только сигналы лишь из одной строки данного списка. Цикл прямого доступа к памяти, в котором это правило не соблюдается, рассмотрен в прило- жении А (см. Рисунок А.2).

По адресованному ему спаду сигнала чтения устройство долж- но выдать на шину данных содержимое адресуемой ячейки и удерживать его, пока не произойдет подъем сигнала. Во время циклов записи процессор выставляет действительные данные несколько позже начала (спада) сигнала записи. Уст-

ройство должно фиксировать для себя эти данные в конце цикла по подъему сигнала. Обращение к портам ввода/вы- вода отличается тем, что сигналы LA[32:17] не используются.

Минимальная длительность цикла определяется чипсетом и может программироваться опциями BIOS Setup заданием тактов ожидания. При этом циклы обращения к памяти ко- роче циклов обращения к портам ввода/вывода. В шине AT для управления минимальной длительностью цикла исполь- зуются также сигналы управления разрядностью передачи:

если устройство поддерживает 16-битные передачи, предпо- лагается, что оно может работать с меньшим количеством тактов ожидания. Этим объясняется, что в Setup длитель- ности циклов ISA задаются раздельно как для памяти и вво- да/вывода, так и для 8- и 16-битных операций.

Если устройство не работает с заданными циклами, оно мо- жет вводить дополнительные такты ожидания, используя сигнал IOCHRDY, но при этом недопустимо удлинять цикл более чем на 15 мкс.

Шина EISA позволяет устройствам работать как в режиме ISA, так и в новых режимах EISA. Из сигналов ISA исполь- зуются линии адреса/данных с расширением их до 32 бит, сигналы прерываний и прямого доступа к памяти и синхро- низации. Для своих циклов обмена EISA использует соб- ственный набор управляющих сигналов с обязательной син- хронизацией по

В EISA-цик- лах не используется сигнал SBHE; он заменен сигналами раз- решения байт ВЕ[3:0]. Вместо общего сигнала AEN каждый слот имеет собственный сигнал AENx. К сигналам расшире- ния шины EISA относятся следующие:

LA[23:16] - опережающие сигналы адреса, требующие за- щелкивания по спаду сигнала BALE.

ж LA[31:24]# - аналогично LA [2:23], но с инверсией.

ВЕ[3:0]# - индикаторы действительности данных в бай- тах 0-3 при EISA-цикле.

М/Ю# - обращение к памяти (1) или портам (0) EISA.

m W/R# - запись (1) или чтение (0) EISA.

ЕХ16#, ЕХ32# - индикаторы разрядности ресурсов.

т SI-BURSTS - адресуемое устройство поддерживает пакет- ный режим обмена.

ж MSBURST - уведомление устройства, подавшего сигнал SLBURST, о намерении инициировать пакетный обмен.

ва LOCK# - обеспечение исключительного права доступа активного EISA Bus-Master к памяти или портам.

ss EXRDY - готовность EISA-устройства; аналогично сигна- лу IOCHRDCY.

STARTS - отмечает начало цикла EISA-доступа. Во вре- мя действия этого сигнала фиксируется адрес и опреде- ляется тип обращения.

CMD# - задает временные параметры цикла; действует после сигнала STARTS.

MREQx# - EISA Bus-Master слота "х" запрашивает управление шиной.

МАКх# - EISA Bus-Master слота "х" получает управле- ние шиной от арбитра.